-

[OS] Virtual Address, Page Table, PML4ComputerScience/OS 2024. 3. 16. 20:34728x90

pintOS 과제를 하던 중 Page Table 말고도 여러 가지 개념들이 나와서 정리를 한번 하고 가야 할 것 같아서 글을 쓴다.

Virtual Address

프로세스가 메모리에 접근할 때 사용하는 주소이다.

OS는 가상 주소를 사용해서 프로세스가 서로의 메모리 공간을 침범하지 않도록 격리한다.

OS는 프로세스로 하여금 전체 메모리 공간을 사용할 수 있다고 '속인다' 또는 '환상'을 제공한다.

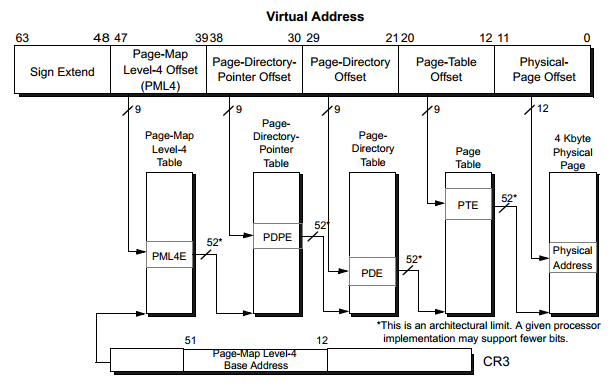

x86-64 아키텍처에서의 가상 주소 구성

x86-64 아키텍처에서 가상 주소는 64비트로 구성되어 있고, 여러 단계의 페이지 테이블을 통해 물리 메모리 주소로 변환된다.

대부분의 x86-64 시스템은 실제로 48비트 혹은 57비트 가상 주소를 사용하고, 이는 CPU나 OS별로 다르다.

출처: superuser - 최상위 비트(47번째 비트)는 48번째 비트부터 63번째 비트까지를 사인 확장(sign extension)함으로써 사용된다.

즉, 47번째 비트가 0이면 48-63비트는 모두 0이 되고, 47번째 비트가 1이면 48-63비트는 모두 1이 된다.

이는 가상 주소 공간을 "양의" 공간과 "음의" 공간으로 나눈다.

-> 이렇게 나누는 이유는 나중에 더 알아보자 - 나머지 0~48비트는 페이지 테이블을 인덱싱 하는데 사용되며 각 페이지 테이블 단계에서 특정 비트 범위가 사용된다.

- PML4 Index

39-47비트 (9비트), 가장 상위 레벨의 페이지 맵 레벨 4(PML4) 테이블을 인덱싱하는 데 사용된다. - PDPT Index

30-38비트 (9비트), 페이지 디렉토리 포인터 테이블(PDPT)을 인덱싱하는 데 사용된다. - PD Index

21-29비트 (9비트), 페이지 디렉토리(PD)를 인덱싱하는 데 사용된다. - PT Index

12-20비트 (9비트), 페이지 테이블(PT)을 인덱싱하는 데 사용된다. - Page Offset

0-11비트 (12비트), 페이지 내에서의 실제 오프셋(위치)을 나타낸다.

표준 페이지 크기가 4KB인 경우, 이 오프셋을 통해 페이지 내의 정확한 주소를 지정할 수 있다.

- PML4 Index

Page Table

가상 주소를 물리 주소로 변환하는데 사용하는 자료구조이다.

테이블은 여러 페이지 테이블 엔트리(Page Table Entries; PTEs)로 구성된다.

각 엔트리는 가상 페이지를 물리 메모리의 특정 페이지에 매핑한다.

Page Table Entry

페이지 테이블 엔트리는 가상 페이지와 그에 매핑된 물리 페이지의 매핑을 정의한다.

엔트리에는 물리 주소, 접근 권한, 사용 여부, 변경 여부 등의 정보가 포함된다.

Page Table Entry의 구성

- 물리 주소 필드

매핑된 물리 페이지의 주소를 저장한다.

일반적으로 x86-64 아키텍처는 4KB 크기의 페이지를 사용하기 때문에,

물리 주소의 하위 12비트는 페이지 내 오프셋을 나타내고 나머지 상위 비트는 물리페이지의 주소를 나타낸다. - 프레젠트 비트(present bit)

해당 페이지가 물리 메모리에 존재하는지에 대한 여부를 나타낸다.

1이면 페이지가 메모리에 존재하고, 0이면 존재하지 않음을 나타낸다. - 읽기/쓰기 비트(read/write bit)

읽기 전용인지, 쓰기 전용인지 여부를 나타낸다.

1이면 쓰기가 허용되고, 0이면 읽기 전용이다. - Write through bit

쓰기 연산 시 캐싱 정책을 나타낸다.

쓰기 작업이 메모리에 직접 반영될지, 아니면 캐시를 통해 처리될지 결정된다. - Cache disabled bit

해당 페이지에 대한 캐싱이 비활성화 되어있는지 여부를 나타낸다. - 사용자/슈퍼바이저 비트(user/supervisor bit)

페이지에 접근할 수 있는 권한 수준을 나타낸다.

1이면 사용자 모드에서도 접근 가능하고, 0이면 커널 모드에서만 접근 가능하다. - 액세스 비트(accessed bit)

페이지가 최근에 접근되었는지 여부를 나타낸다.

이 비트를 통해 페이지 교체 알고리즘에 활용할 수 있다.

ex) LRU(Least Recently Used) - Global Bit

페이지가 모든 프로세스에 대해 글로벌하게 적용되는지 여부를 나타낸다.

이 비트를 사용하여 커널 모드의 페이지를 모든 프로세스에서 공유할 수 있다. - No Execute(NX)

실행 금지 비트로, 해당 페이지에서 코드 실행을 금지할지 여부를 결정한다. - 더티 비트(dirty bit)

페이지가 쓰기 작업으로 인해 변경되었는지를 나타낸다.

페이지의 변경 사항을 디스크에 백업할 필요가 있는지 결정하는 데 사용될 수 있다.

PML4

x86-64 아키텍쳐에서 사 용퇴는 페이지 테이블의 최상위 레벨이다.

4단계 테이블 구조의 첫 번째 레벨로, 가상 주소를 물리 주소로 매핑하는 과정에서 시작점 역할을 한다.

x86-64 아키텍쳐에서의 페이지 테이블 구조

- PML4(Page Map Level 4)

4단계 페이지 테이블 구조의 최상위 레벨로, 512개의 엔트리를 포함할 수 있다.

각 엔트리는 PDPT를 가리키는 포인터이다.

가상 주소의 상위 비트가 PML4에서 해당 엔트리를 찾는 데 사용된다. - PDPT(Page Directory Pointer Table)

또한 512개의 엔트리를 포함할 수 있다.

각 엔트리 역시 PD를 가리키는 포인터이다.

가상 주소에서 또 다른 부분이 PD에서 해당 엔트리를 찾는데 사용된다. - PD(Page Directory)

역시 512개의 엔트리를 포함하고, PT를 가리키는 포인터를 포함한다.

가상 주소에서 또 다른 부분이 PD에서 해당 엔트리를 찾는 데 사용된다. - PT(Page Table)

가상 주소를 물리 주소로 매핑하는 실제 매핑을 포함하는 최종 단계의 테이블이다.

512개의 엔트리는 물리 메모리 내의 실제 페이지를 가리킨다.

가상 주소의 마지막 부분은 PT에서 해당 엔트리를 찾는데 사용되고,

엔트리 내에 저장된 물리 주소 정보를 통해 최종 물리 주소가 결정된다.

가상 주소에서 물리 주소로의 변환 과정

- PML4에서 시작

CPU는 가상 주소의 상위 비트를 사용하여 PML4에서 해당 엔트리를 찾는다. - PDPT로 이동

PML4 엔트리는 PDPT의 주소를 가리키고, 가상 주소의 다음 세그먼트는 PDPT에서 해당 엔트리를 찾는 데 사용된다. - PD 찾기

PDPT 엔트리는 PD의 주소를 가리키고, 가상 주소의 다음 부분은 PD에서 해당 엔트리를 찾는데 사용된다. - PT로 이동

PD 엔트리는 PT의 주소를 가리키고, 가상 주소의 다음 부분은 PT에서 해당 엔트리를 찾는 데 사용된다. - 물리 주소

PT 엔트리는 실제 물리 조스의 기본 주소를 제공하고, 가상 주소의 마지막 부분은 물리 페이지 내에서의 오프셋을 나타낸다.

결국 약 48비트 가상 주소는 페이지 테이블의 인덱싱 번호이므로, 이를 분석하여 물리 주소가 매핑된 최종적인 페이지 테이블을 찾아가는 것이라고 볼 수 있는데, 맨 처음 가상 주소가 CPU에 전달되면 어떻게 분석되는지 궁금해졌다.

가상주소에서 물리 주소로 변환 과정에서의 MMU의 역할

메모리 관리 장치(MMU)는 가상 주소를 물리 주소로 변환하는 중심적인 역할을 한다.

MMU는 CPU와 실제 메모리 사이에 위치하며, CPU가 실행하는 모든 메모리 접근 요청을 처리한다.

CPU가 가상 주소를 사용하여 메모리에 접근하려고 할 때, MMU는 이 가상 주소를 물리 주소로 변환하는 작업을 수행한다.- 가상 주소 분석

MMU는 CPU로부터 전달받은 가상 주소를 분석하여, PML4 인덱스, PDPT 인덱스, PD 인덱스, PT 인덱스, 그리고 페이지 오프셋으로 분리한다. - 페이지 테이블 탐색

MMU는 루트 페이지 테이블인 PML4에서 시작하여, 가상 주소에 해당하는 각 인덱스를 사용해 PDPT, PD, PT를 차례로 탐색한다. 각 단계에서 해당 인덱스에 맞는 엔트리를 찾아 다음 단계의 페이지 테이블 주소를 얻는다. - 물리 주소 도출

최종적으로 PT에서 해당 페이지 테이블 엔트리를 찾은 후, 이 엔트리에 저장된 물리 주소 정보와 가상 주소의 페이지 오프셋을 결합하여 최종 물리 주소를 도출한다.

이 과정에서 MMU는 필요에 따라 TLB(Translation Lookaside Buffer)를 사용하여 변환 과정의 효율을 향상한다고 한다.

너무 깊게 들어가지 않기 위해 간략하게 TLB에 대해서 설명하자면,

TLB는 최근에 사용된 가상 주소와 해당하는 물리 주소 매핑을 캐싱하는 작은 메모리이다.

가상 주소를 물리 주소로 변환할 때, MMU는 먼저 TLB에서 해당 매핑을 검색하고, 만약 TLB 내에 존재한다면 페이지 테이블을 탐색하는 과정 없이 바로 물리 주소를 얻는다. TLB 미스가 발생할 경우에만 전체 페이지 테이블 탐색 과정을 진행한다.

TLB도 중요한 개념이기 때문에 나중에 더 자세히 다룰 수 있으면 다뤄봐야겠다.

'ComputerScience > OS' 카테고리의 다른 글

[OS] 주소 공간, 메모리 관리 API, 주소 변환의 원리 (1) 2024.03.26 [OS] Swap, File-backed Page, DMA (0) 2024.03.22 [OS] File Descriptor (0) 2024.03.18 [OS] User mode & Kernel mode (0) 2024.03.12 [OS] 32 bit OS vs 64 bit OS (1) 2024.03.12 - 최상위 비트(47번째 비트)는 48번째 비트부터 63번째 비트까지를 사인 확장(sign extension)함으로써 사용된다.